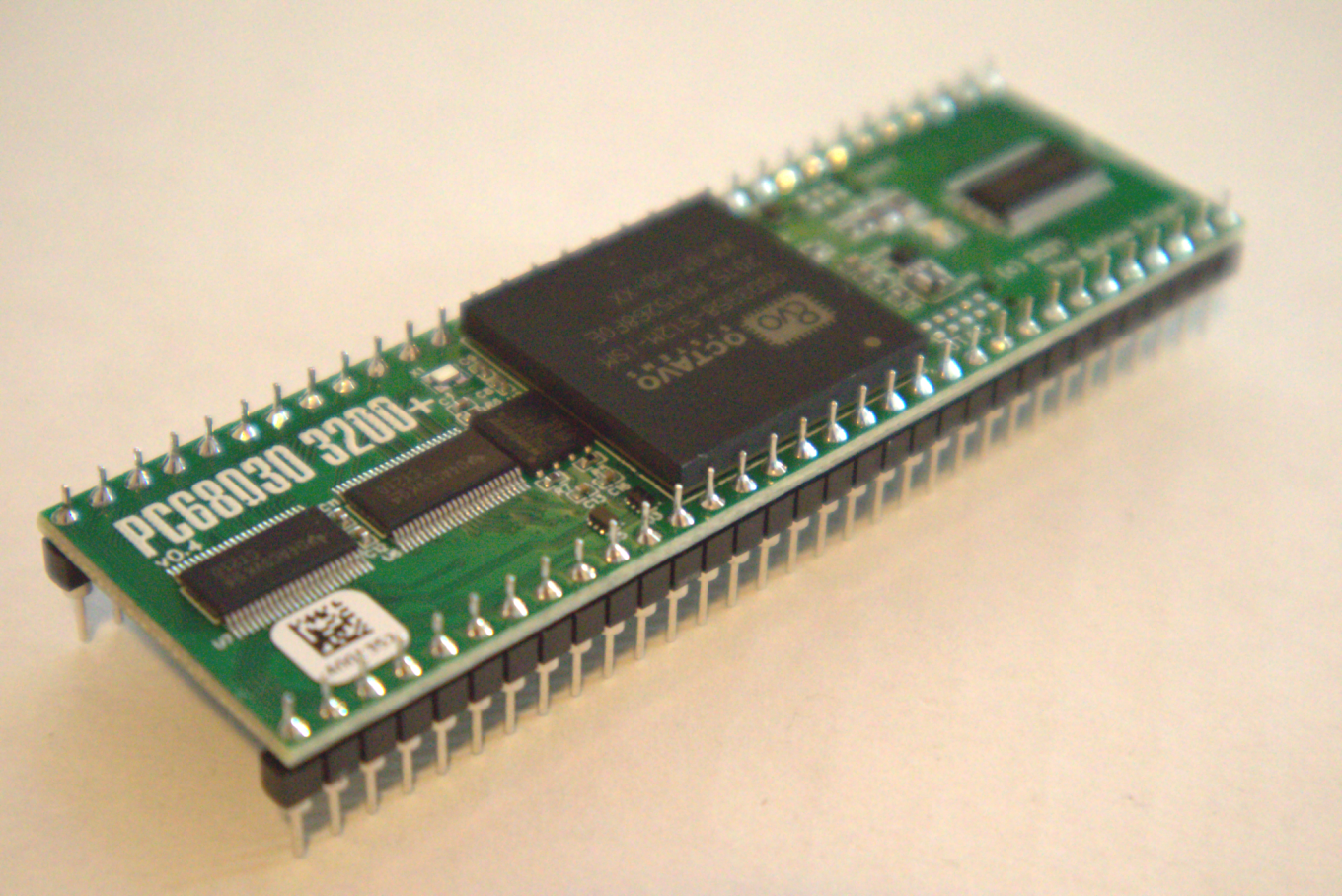

The v0.5 (BETA) is officially done of Buffee and this is the changes made:

– power in to support 2.7V to 5.5V operation (alpha only supports down to 4.5V)

– SPI flash data pins to support booting; length matched for fun (this doesn’t prevent alpha’s from running, just booting from flash)

– new feature: CLK supports both input (async) and output (sync)

– new feature: replaced fixed logic with programmable Green PAK “SPLD”; this will allow the Buffee team to tweak and repurpose the IO logic

– added I2C to UART header for SPLD programming

– GPMC has all fast logic pinned out to SPLD (e.g., FCx and DTACK)

– GPMC has all slow logic is fed through PRU (e.g., VPA and BG)

– JTAG RESET actually resets CPU in addition to TRST (which doesn’t)

– removed some passives and basically rerouted the whole board

This is the the right JTAG/UART cables that you need to order to connect to Buffee:

If you have further questions go to the Buffee Discord Server. Buffee will become the CPU+MEM accelerator for any 68000 CPU socket computer or console. Amitopia Amiga Magazine is now donating a bit every month until the Buffee project is mature enough to be sold. I do this because it is important for this project to be done.